Ngày 2/2/2018, nghiên cứu sinh Phan Hải Phong đã bảo vệ thành công cấp cơ sở luận án tiến sỹ với tiêu đề "Giải pháp tối ưu công suất tiêu thụ cho các kiến trúc mạng trên chip". Chuyên ngành: Kỹ thuật điện tử. Luận án được thực hiện tại Phòng thí nghiệm trọng điểm Hệ thống tích hợp thông minh (SISLAB).

Ngày 2/2/2018, nghiên cứu sinh Phan Hải Phong đã bảo vệ thành công cấp cơ sở luận án tiến sỹ với tiêu đề "Giải pháp tối ưu công suất tiêu thụ cho các kiến trúc mạng trên chip". Chuyên ngành: Kỹ thuật điện tử. Luận án được thực hiện tại Phòng thí nghiệm trọng điểm Hệ thống tích hợp thông minh (SISLAB).

Thông tin tóm tắt về luận án có thể xem tại đây (hoặc PDF).

SISLAB chúc mừng nghiên cứu sinh.

Kể từ khi vi mạch tích hợp đầu tiên được phát minh vào năm 1958 thì cho đến nay công nghệ vi mạch đã thực sự bùng nổ và có những bước phát triển nhanh chóng chỉ trong một quãng thời gian ngắn. Trong những năm gần đây, khi kỹ sư thiết kế tiếp cận với việc xây dựng các hệ thống trên chip (SoC: System on Chip) phức tạp thì quy trình thiết kế vi mạch theo hướng giảm thiểu năng lượng tiêu thụ đã trở thành một thách thức lớn. Các kỹ sư thiết kế đã áp dụng nhiều phương pháp khác nhau từ giải pháp phần mềm đến kiến trúc phần cứng ở mọi bước của quá trình thiết kế để có thể tối ưu hoá được năng lượng tiêu thụ trên vi mạch.

Bên cạnh đó, sự phát triển của các SoC phức tạp cũng đã thúc đẩy một mô hình truyền thông trên chip phát triển để thay thế cho các mô hình truyền thông truyền thống trước đó. Đó chính là mô hình của các mạng trên chip (NoC: Network on Chip). Tuy nhiên, cùng với sự gia tăng về số lượng lõi IP được tích hợp trên một chip thì năng lượng cần cung cấp cho NoC cũng chiếm một phần lớn năng lượng của toàn hệ thống. Chính vì vậy, việc nghiên cứu và phát triển các hệ thống mạng trên chip tiêu thụ ít năng lượng hơn đã và đang là một hướng nghiên cứu dành được nhiều sự quan tâm.

Từ những phân tích và đánh giá như trên, luận án này đã đặt ra mục tiêu là tìm hiểu, nghiên cứu và đề xuất giải pháp tối ưu công suất tiêu thụ cho các kiến trúc mạng trên chip. Với mục tiêu như vậy, luận án này tập trung vào một số nội dung nghiên cứu cụ thể như sau:

- Nghiên cứu về một số vấn đề cơ bản của mô hình mạng trên chip như: tô-pô mạng, cơ chế truyền thông, các thuật toán định tuyến, vấn đề điều khiển luồng dữ liệu...

- Nghiên cứu các phương pháp, kỹ thuật đang được ứng dụng hiện nay để thiết kế các vi mạch tích hợp với công suất tiêu thụ thấp. Tìm hiểu các kỹ thuật cũng như các quy trình thiết kế theo hướng tối ưu hóa năng lượng tiêu thụ áp dụng cho các hệ thống trên chip, mạng trên chip.

- Nghiên cứu, tìm hiểu một số kiến trúc mới hoặc một số thuật toán định tuyến mới được phát triển gần đây nhằm giải quyết vấn đề giảm thiểu năng lượng tiêu thụ cho các mạng trên chip.

- Đề xuất một số giải pháp hoặc kỹ thuật mới để xây dựng một mô hình mạng trên chip theo hướng tối ưu hóa về công suất tiêu thụ.

- Áp dụng các giải pháp, kỹ thuật này vào mô hình mạng trên chip dạng 2D-mesh đang được phát triển tại Phòng thí nghiệm trọng điểm Hệ thống tích hợp thông minh (SISLAB), Trường Đại học Công nghệ. Đánh giá và phân tích hiệu quả của giải pháp đề xuất.

Để có thể đưa ra được một giải pháp đúng đắn theo mục tiêu nghiên cứu đã đề ra, luận án này đã áp dụng các phương pháp nghiên cứu như sau để có thể tiếp cận, phân tích và xây dựng được một mô hình phù hợp:

- Tìm hiểu tổng quan về lý thuyết và các công trình liên quan đến mô hình mạng trên chip cũng như các vấn đề cơ bản của loại mô hình truyền thông này. Đồng thời, tìm hiểu tổng quan lý thuyết về các kỹ thuật và phương pháp tối ưu năng lượng tiêu thụ khi thiết kế các vi mạch tích hợp. Nghiên cứu các phương pháp hoặc kỹ thuật thiết kế được áp dụng để xây dựng các mô hình mạng trên chip theo hướng tối ưu hóa năng lượng tiêu thụ.

- Xây dựng các phương án nhằm phân tích, đánh giá hoạt động của một mạng trên chip ở mức hệ thống để rút ra các đặc trưng liên quan đến năng lượng tiêu thụ. Từ đó tìm ra được các yếu tố ảnh hưởng đến vấn đề năng lượng tiêu thụ của toàn hệ thống.

- Đề xuất giải pháp điều khiển bằng phần cứng ở mức thấp để tối ưu hóa năng lượng tiêu thụ của hệ thống dựa trên các kỹ thuật tiên tiến. Mô hình hoá, mô phỏng và kiểm chứng kiến trúc đề xuất bằng cách áp dụng lên một hệ thống mạng trên chip dạng 2D-mesh để khẳng định hoạt động về mặt chức năng đề ra.

Với các kết quả cụ thể được trình bày trong Chương 3 và Chương 4, trong tầm hiểu biết của nghiên cứu sinh, có thể kết luận luận án đã đạt được mục tiêu nghiên cứu đặt ra. Các kết quả mà luận án đạt được tập trung vào ba nội dung chính sau:

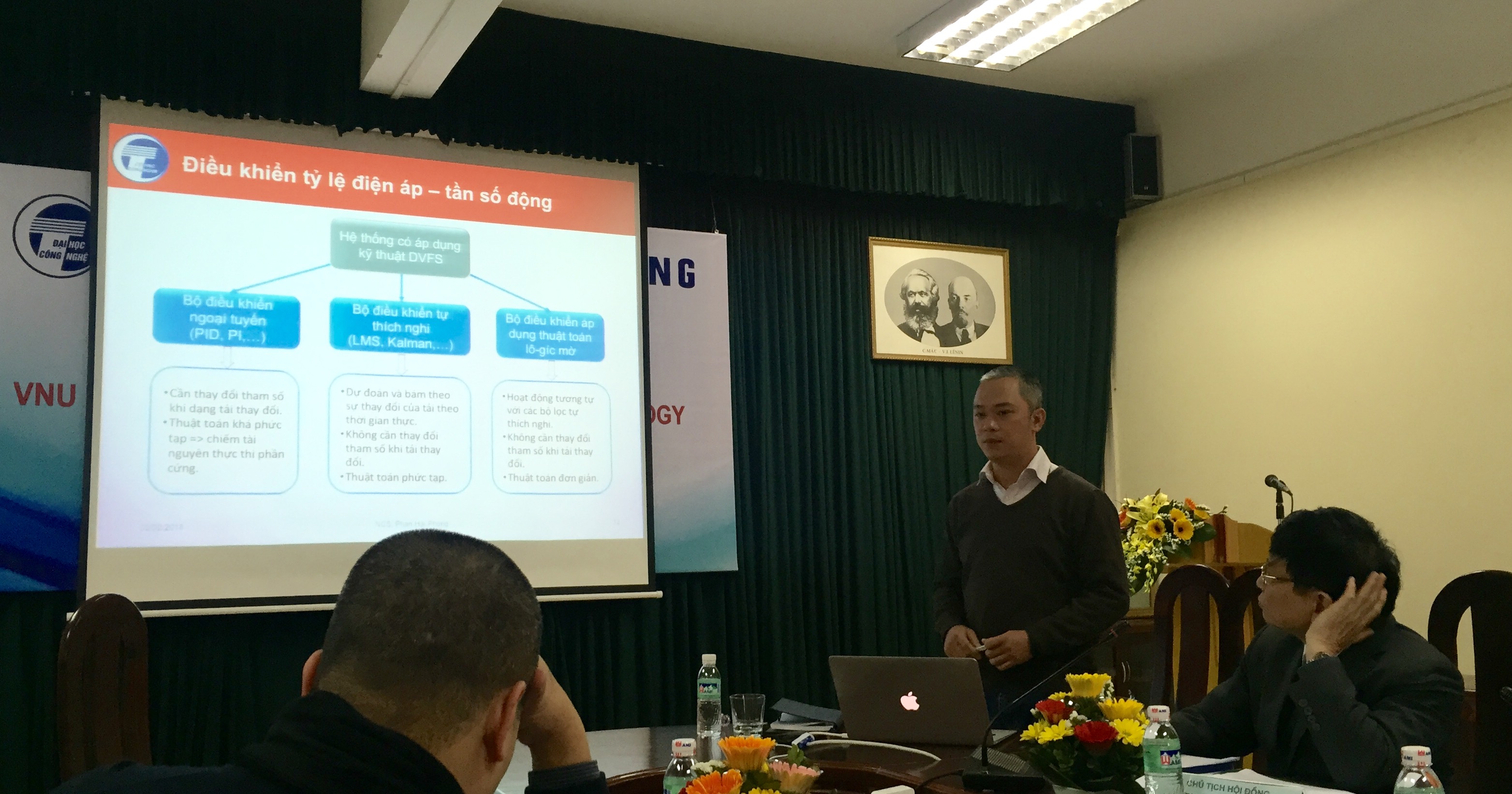

- Đề xuất được một giải pháp dựa trên phương pháp điều khiển tỷ lệ tần số - điện áp động (DVFS) và thuật toán lô-gíc mờ để tối ưu được năng lượng tiêu thụ cho kiến trúc truyền thông mạng trên chip dạng 2D-mesh.

- Mô hình hoá và thực thi giải pháp được đề xuất dưới dạng phần cứng bằng ngôn ngữ mô tả phần cứng VHDL. Các khối thành phần của giải pháp đều được mô hình hoá ở mức chuyển dịch thanh ghi (RTL: Register Transfer Level) và đã được mô phỏng, kiểm chứng hoạt động lô-gíc bằng phần mềm mô phỏng ModelSim (Mentor Graphics).

- Đề xuất phương án cho phép đánh giá hiệu quả tiêu thụ năng lượng của mạng trên chip ở mức hệ thống khi có áp dụng các kỹ thuật điều khiển DVFS khác nhau thông qua nền tảng ORION, một mô hình cho phép ước lượng năng lượng tiêu thụ của mạng trên chip với độ chính xác cao.

| Attachment | Size |

|---|---|

| 958.86 KB | |

| 826.76 KB | |

| 623.22 KB |

- Log in to post comments